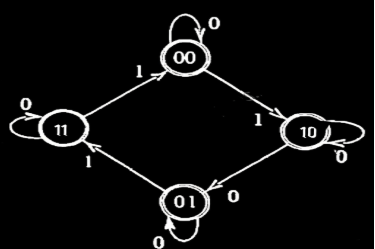

Design MOD-7 counter with state and timing diagram.

Marks: 5

Year: 2019 Final TU FOHSS

MOD-7 Counter Definition: A MOD-7 counter is a counter that counts from 0 to 6 (7 states) and then resets to 0. Type: - Can be synchronous or asynchronous. - Requires 3 flip-flops (since 2³ = 8